Android Vhdl Simulator With Many Choices

Yes VeriWell is the same simulator that was sold by. Download VHDL and verilog for Android to app is a free programming reference application for VHDL and Verilog.

In 2003 ModelSim 58 was the first simulator to begin supporting features of the Accellera SystemVerilog 30 standard.

Android vhdl simulator. VHDL-1987-1993-2002-2008 V2001 SV2005 SV2009 SV2012. VeriWell Verilog Simulator. VHDL for Simulation – LIVE ONLINE Programmable logic devices like FPGAs have been established in the daily life.

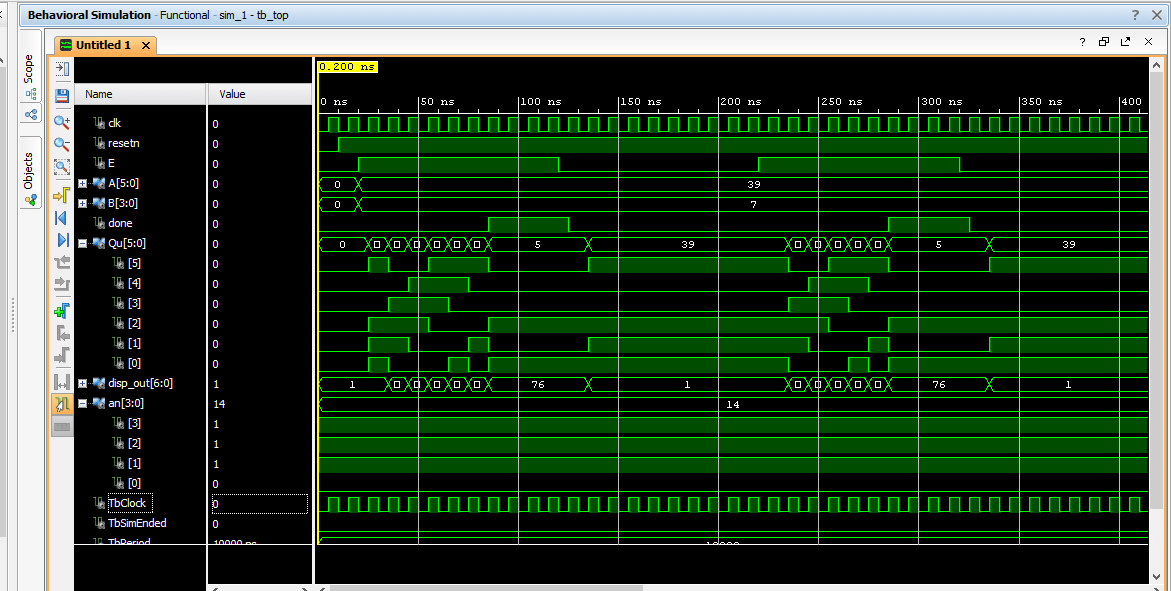

It runs Android Marshmallow and thats still relatively new compared to. For simulation ModelSim-Altera Starter Edition is a free version of ModelSim provided by Altera and is very user friendly and widely used. It is very important to check that the code you wrote is behaving the way you expect it to behave.

MyCAD-SDS supports various netlist formats such as VHDL verilog EDIF and XNF. With the GUI design and code generation it already reduced the code writing. Dieser android Simulator ermöglicht es Benutzern Bilder im Batch zu senden kann man suchen und abonnieren WeiChat Publikumszahlen großen Bildschirmauflösung hohe Leistung und es enthält PC Seite Mate und mobile app.

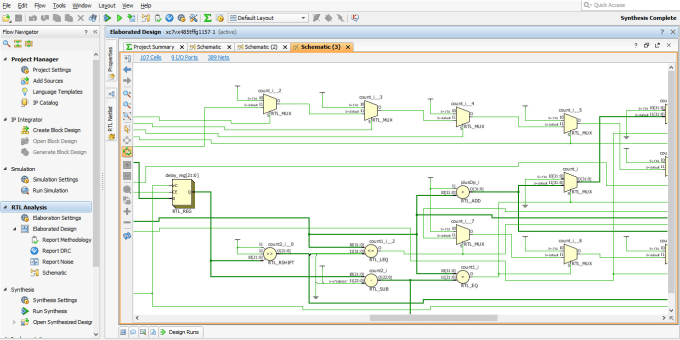

VHDL Simulator VHDL Synthesizer Schematic Generator Schematic Editor Logic Simulator FPGA Prototyper. Play with it you will find answers. Most simulators work on Linux too.

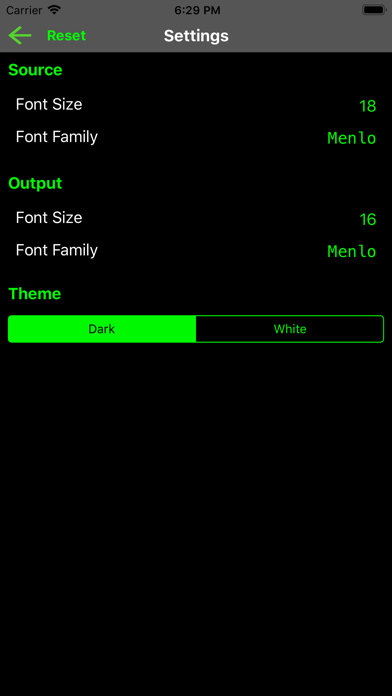

It has a build in editor with VHDL color coding so you can do editing compile and simulation from within ModelSim. Ghdl-yosys-plugin VHDL synthesis based on ghdl. Ghdl-language-server Language server based on ghdl NewLisp 6 36 9 0 Updated Apr 19 2021.

VHDL 20089387 simulator simulator compiler hardware llvm vhdl gcc ghdl VHDL GPL-20 228 1309 229 4 issues need help 14 Updated Apr 23 2021. GHDL fully supports the 1987 1993 2002 versions of the IEEE 1076 VHDL standard and partially the latest 2008 revision well enough to support fixed_generic_pkg or float_generic_pkg. It is still improving.

Remix OS Player by Jide is one of the newer Android emulators for PC comparatively speaking. The IDE might come without a built-in simulator and the simulator might come without a GUI. Thats what you are looking for.

Alliance CAD System is a free set of EDA tools and portable cell libraries for VLSI design. Android-Emulatoren bringen das beliebte Smartphone-Betriebssystem auf Ihren PC. This is done with a simulator.

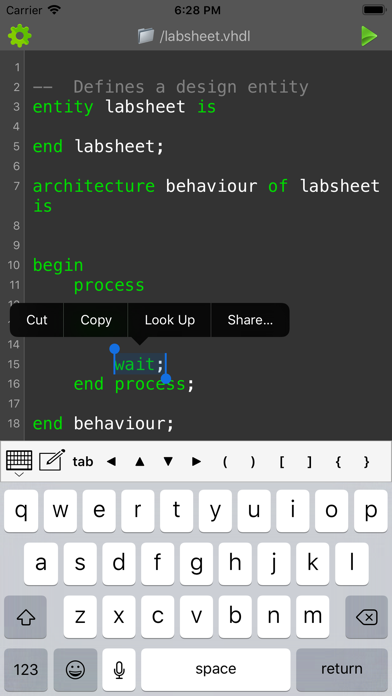

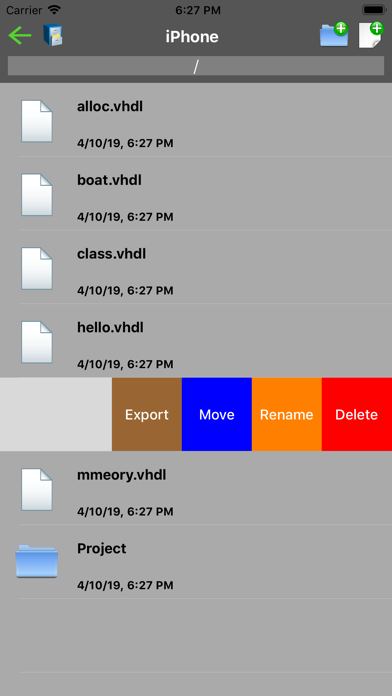

You dont want to design whole project on android tablet. This App provides sample programs of VHDL and verilog programmingyou can use these programs as reference in learning basic concepts Keywords are highlightedSyntax highlighting HDL — Hardware Description Language You can also share the programs using share icon above programs It also has explanation and examples of reserved words of VHDL. It includes VHDL simulator RTL synthesis place and route netlist extractor DRC layout editor.

Jedoch unterstützt nicht die Entwickler es hat keine Kamera-Integration hat keine app Sync keine Integration von Sensoren und bietet keine Unterstützung für Mac OS. The simulator that is most popular in the commercial world is called Modelsim and it is made by Mentor Graphics. It supports nearly all of the IEEE1364-1995 standard as well as PLI 10.

So können Sie Ihre liebsten Apps und Games ganz einfach auf einem Windows-Computer verwenden. They can be found in mobile phones IoT devices cars or cloud data centers. You can just focus on your algorithm code.

Altera Quartus 2. It covers the design flow from VHDL up to layout. GHDL allows you to compile and execute your VHDL code directly in your PC.

Netlist import and export logic simulation and For FPGA prototyping MyProtor supports both Altera and Xilinx FPGA series and runtime debugging. Part of your project can be done easily with Robei and the simulation speed is fast enough. If youre looking for a simulator here is a list of free VHDL simulators with download links.

The app contains Basic VHDL Programs. VeriWell is a full Verilog simulator. Simulation is a critical part of any design.

The original Modeltech VHDL simulator was the first mixed-language simulator capable of simulating VHDL and Verilog design entities together. GHDL is an open-source simulator for the VHDL language. Vivado Xilinx and Quartus Altera are synthesis tools which can transform your VHDL.

Vhdl Code For Seven Segment Display On Basys 3 Fpga Fpga4student Com Seven Segment Display Coding Segmentation

Vhdl And Verilog For Android Apk Download

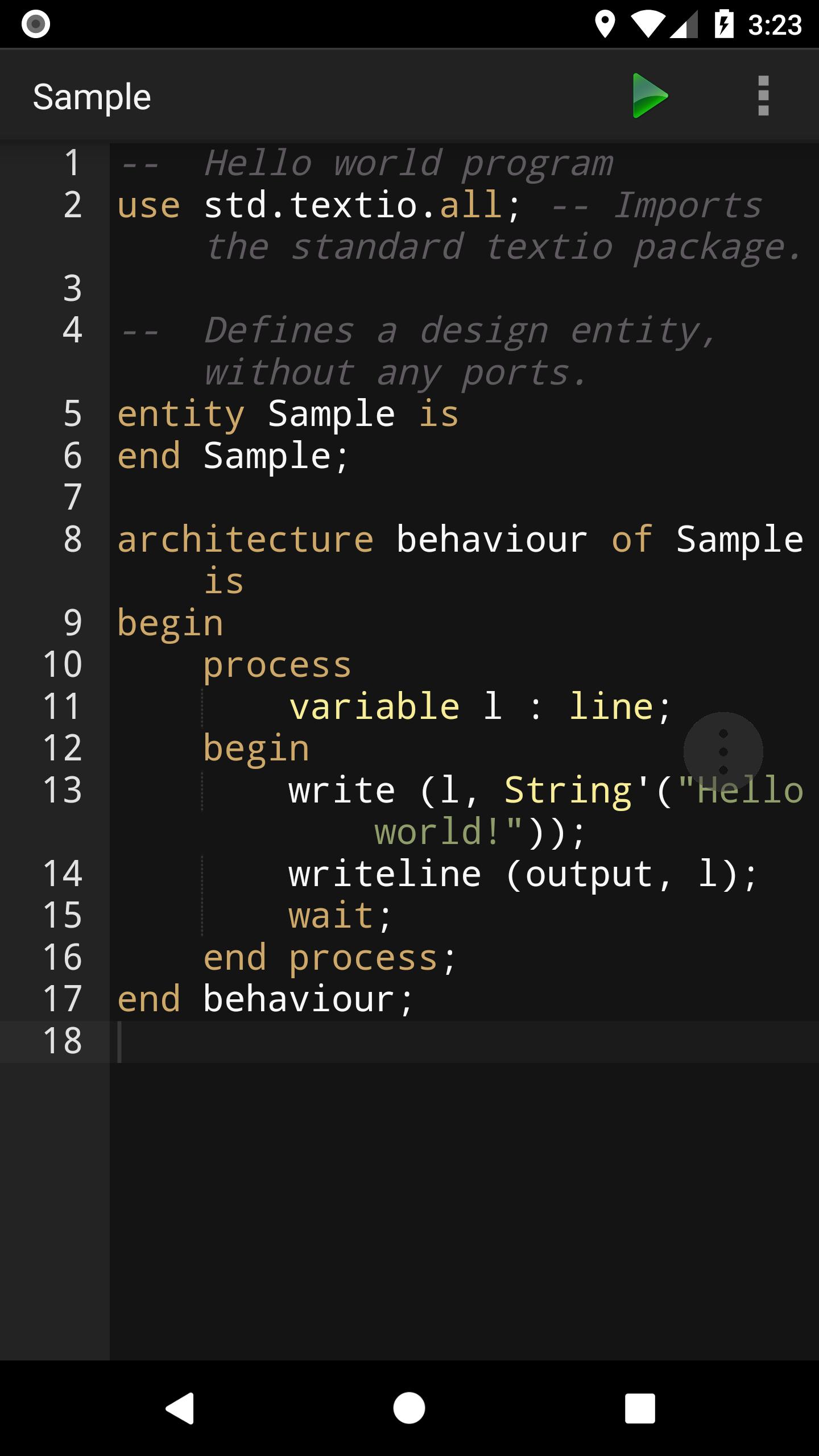

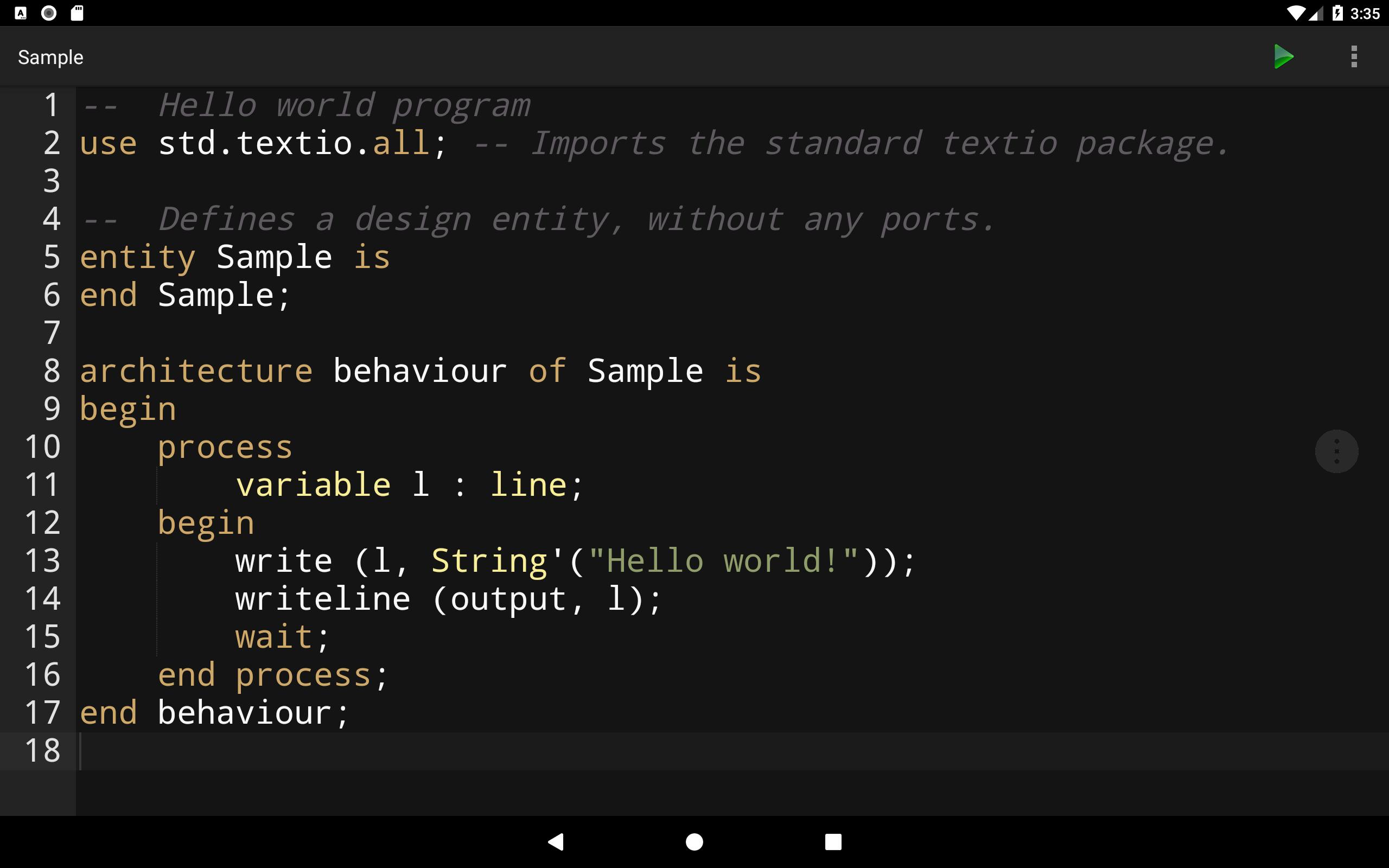

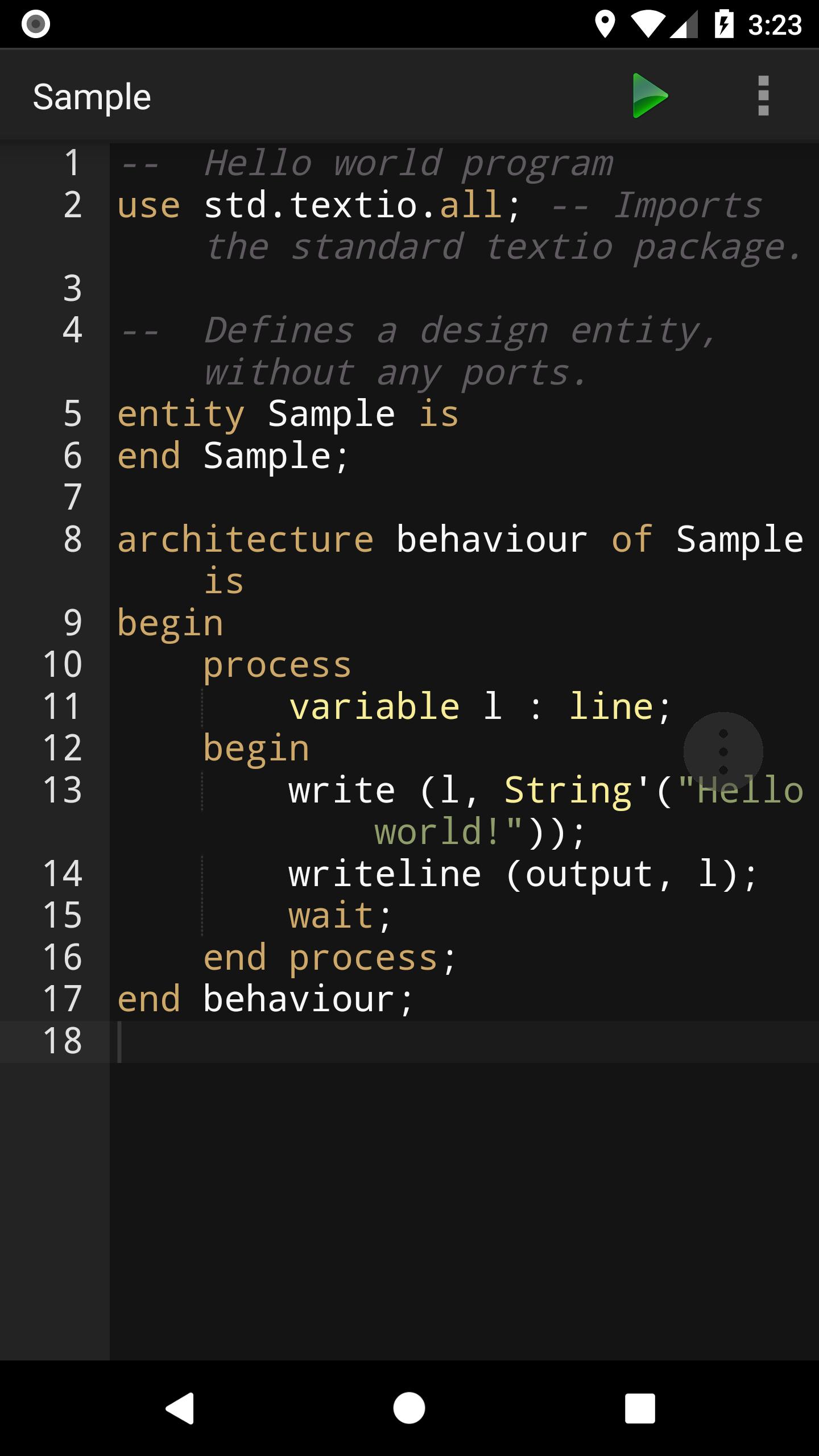

Vhdl Programming Compiler For Android Apk Download

Vhdl Compiler For Android Download Free Latest Version Mod 2021

Vhdl Compiler For Android Download Free Latest Version Mod 2021

Vhdl Programming Compiler For Android Apk Download

Vhdl Compiler For Android Download Free Latest Version Mod 2021

Do Vhdl Verilog Coding For You By Rashidkhan506 Fiverr

Vhdl Simulation Und Synthese Entwurf Digitaler Schaltungen Und Systeme De Gruyter Studium Amazon De Reichardt Jurgen Schwarz Bernd Bucher

Vhdl Code For And Gate Techwithcode Com Coding Knowledge Language

Vhdl Compiler For Android Download Free Latest Version Mod 2021

Vhdl Programming Compiler Apps On Google Play

Do Vhdl Verilog Coding In Vivado Quartus And Modelsim By Rashidkhan506 Fiverr

Engineers Club Vhdl Code For Bcd Adder Block Diagram Diagram Coding

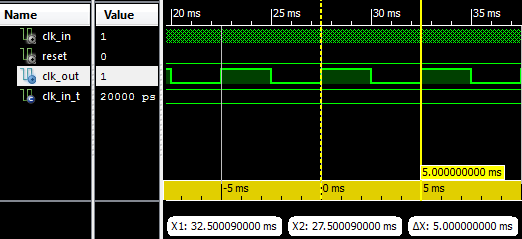

Frequency Divider With Vhdl Codeproject

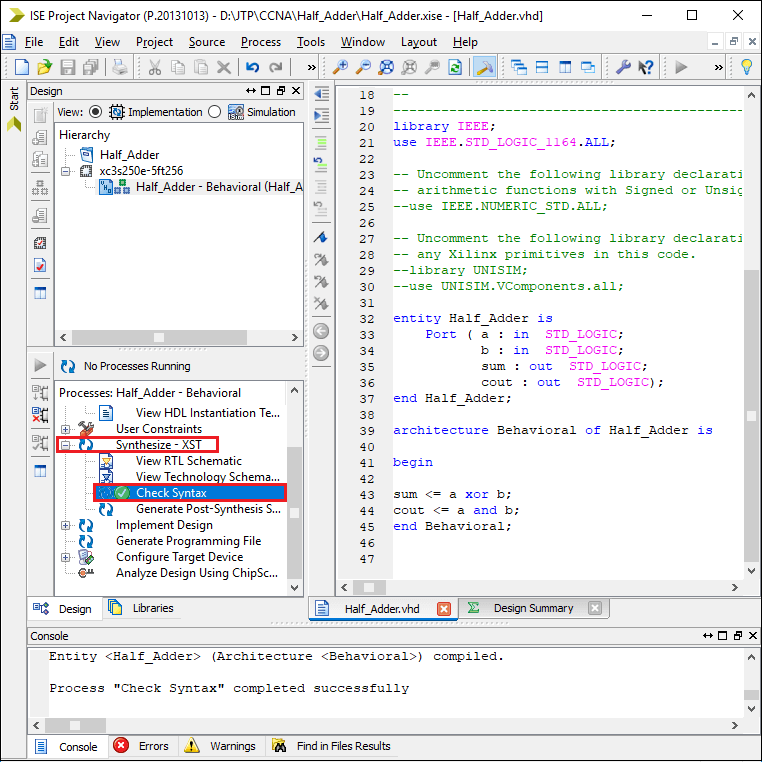

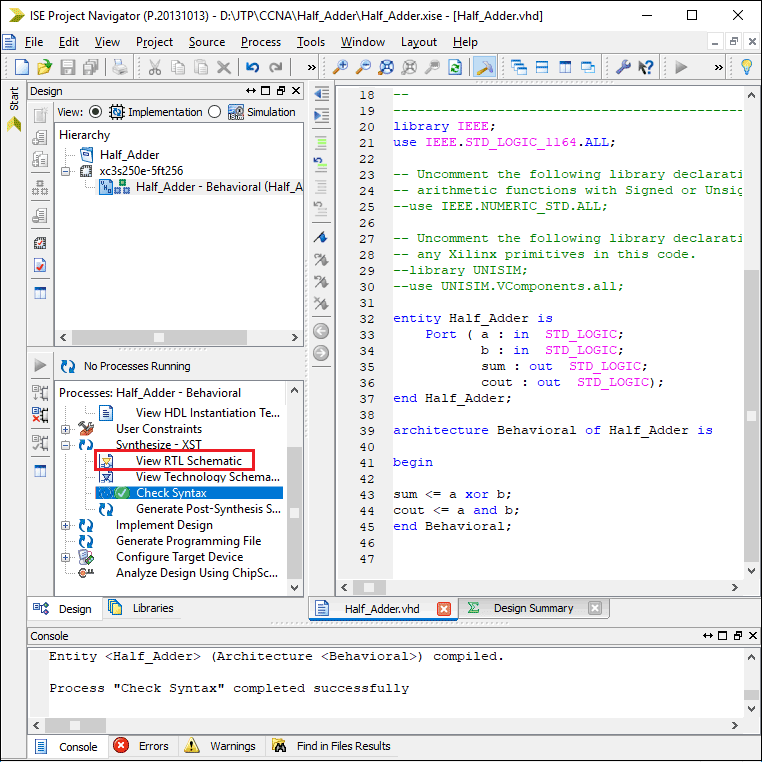

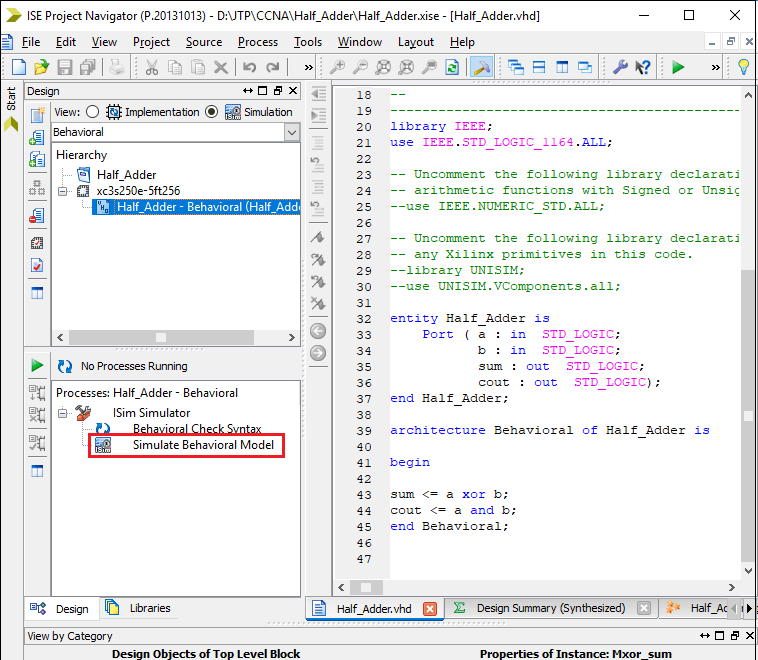

Beginner Learning Ise Half Adder Simulation Vhdl Programmer Sought

Post a Comment for "Android Vhdl Simulator With Many Choices"